ECE 550D: Fundamentals of Computer Systems and Engineering — Fall 2021

Class meeting times and location: TuTh 10:15–11:30AM and 1:45–3:00PM (2 sections) — Hudson Hall 125 and Wilkinson 130

Recitation meeting time and location: F 12:00–1:15PM — FITZPATRICK SCHICIANO B 1466

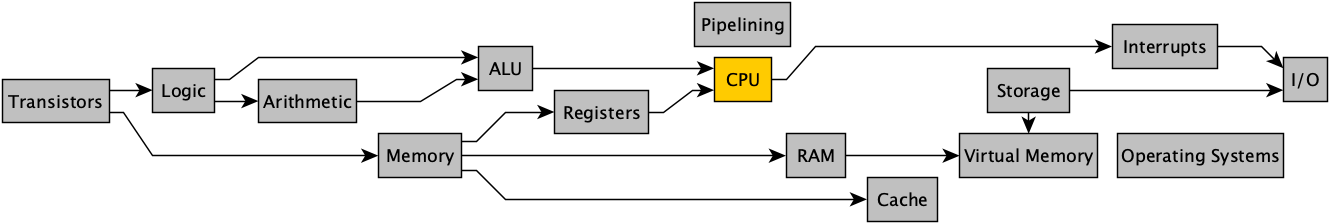

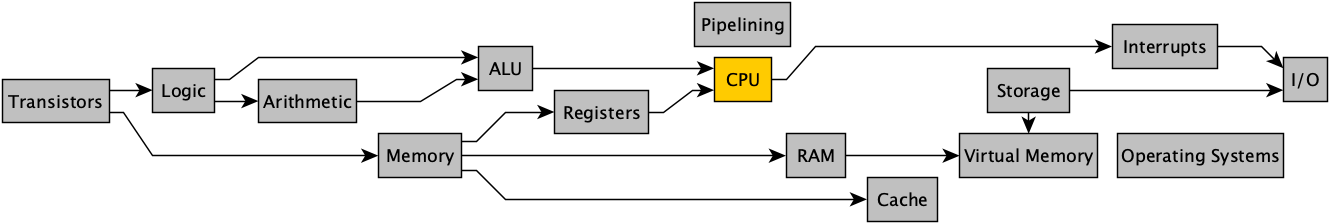

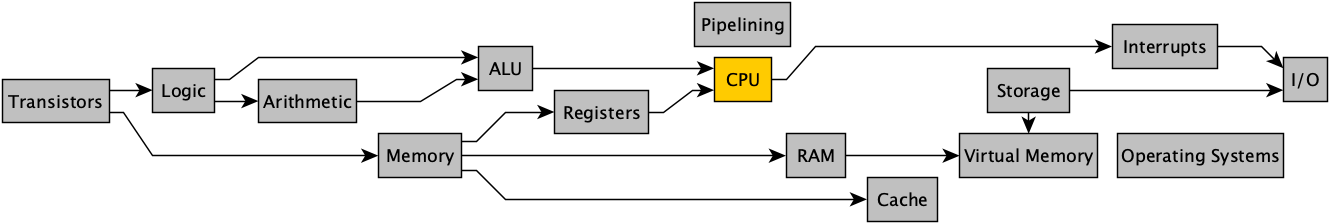

based on a diagram by Dr. Tyler Bletsch

Instructor: Dr. Rabih Younes

Duke e-mail: rabih.younes

Office hours: by appointment (link to make appointments posted on Sakai)

To provide anonymous feedback about anything related to the course, please follow this link (password posted on Sakai).

TAs:

- Wenxin Xu (wx65) — Head TA for projects

- Shiyi Jiang (sj255) — Head TA for homework

- Hanzhou Shen (hs312) — Head TA for recitations

- Ke Chen (kc426) — Head TA for cheating detection

- Libo Zhang (lz200)

- Qishen Wang (qw98)

TA office hours (location: Hudson Hall 214):

- MW: 4:45–6:45

- TuTh: 9–11

- F: 10:30–11:30 & 3:00–4:00

Course Description

Fundamentals of computer systems and engineering for Master's students whose undergraduate background did not cover this material. Topics covered include: Digital logic, assembly programming, computer architecture, memory hierarchies and

technologies, IO, and hardware implementation in HDL. Undergraduates may not take this course, and should take ECE 250D, ECE 353, and/or ECE 356 instead. Instructor: Younes. 3 units. Co-requisite: ECE 551D.

Learning Outcomes

Having successfully completed this course, the student will be able to:

- design combinational and sequential circuits at the transistor (CMOS) and gate/logic levels;

- implement, simulate, and test logic circuits;

- use Verilog hardware description language;

- write programs using Assembly language;

- describe and analyze how computer memory operates;

- describe the basic operations of IO devices, interrupts, and exceptions; and

- design, implement, and test a processor.

Textbook and Other Course Material

Textbook not required. The suggested textbook is: David A. Patterson and John L. Hennessy. Computer Organization and Design: The Hardware/Software Interface, 5th edition, Morgan-Kaufmann. (Amazon,

AddAll) —

(Not the "ARM" edition or the "Revised Printing").

All other material will be posted on Sakai. Slides will be posted before class time so that you can take notes on them if you would like to.

Grading Policy

- Recitations (10%): Recitations are sessions for hands-on practice using Quartus and Modelsim. Grades are based on completion (must demonstrate working module to TA).

- Homeworks (20%): About 5 homeworks (check the schedule below).

- Exam 1 (15%).

- Exam 2 (15%).

- Project (40%): Checkpoints that build up to implementing a processor.

- NO FINAL EXAM!

- Late policy: Late submissions are not allowed unless you have a valid excuse. In that case, email me about it as soon as possible and wait for a decision (might involve a penalty, depending on the excuse). Refer

to this list of common but unacceptable excuses borrowed from Dr. Bletsch's webpage.

- Regrading policy: Regrade requests must be submitted no later than one week after the assignment grade is released.

Important Notes

***Extremely important advice:

- Start as early as you can! Leave ample time for testing!

- Review class lectures after every class (or before the next one).

- Manage your time well and work on multiple assignments in parallel. Split bigger task into smaller (realistic) ones. Make sure you use a calendar and a to-do list.

- Use Git to keep track of previous versions of your work and use a cloud storage service to back up your work (GitLab, GitHub, etc.).

- Ask questions! We are here to help! We want you to succeed!

We can only grade what we receive. Always check what you are submitting and make sure you submit the right files.

Contacting the instructor and the TAs:

- For questions that can be answered by any TA or the instructor: use Ed Discussion

- To contact a specific TA or the instructor: use email (do not text, facebook, ...)

Misconduct

- Academic misconduct will not be tolerated and will be taken very seriously.

- You are expected to complete the assignments individually unless otherwise stated.

- Students are encouraged to share ideas, learn from each other, and learn from online sources, but cheating is not tolerated.

- Any borrowed design/code/etc. — if allowed to be borrowed — should be properly cited.

- Students suspected violating the Duke Community Standard will be reported.

- In addition to the measures taken by the administration, the affected assignment(s) will receive zero credit, or possibly -100% in extreme cases.

- If you are considering this course of action, please see me instead, and we can work something out! I want every student in my course to be successful.

- Note that programming submissions will be compared to one another and to previous semesters using Stanford's Measure of Software Similarity (MOSS) to detect signs of plagiarism.

Communications Support at Pratt

Graduate Communications and Intercultural Programs (GCIP) offers customized communications support for all graduate students at Pratt. They offer one-on-one coaching in the Graduate Communications Center (GCC) for all communications needs (e.g.,

academic writing, cover letters, presentations, pronunciation, master's theses/projects, PhD dissertations/publication/prelims). Additionally, GCIP offers a communication workshop series to help build specific communication skills throughout the

academic year. Visit this link or email gcc-pratt@duke.edu.

| Week |

Date |

Topic |

Homework |

Project Checkpoints |

Recitation (Friday) |

| 1 |

Tue 8/24 |

Syllabus + Intro |

|

|

|

| 1 |

Thu 8/26 |

Transistors to Gates |

|

|

Quartus + Verilog Intro |

| 2 |

Tue 8/31 |

Combinatorial Logic |

|

|

|

| 2 |

Thu 9/2 |

Digital Arithmetic |

|

|

Adder |

| 3 |

Tue 9/7 |

Digital Arithmetic |

|

|

|

| 3 |

Thu 9/9 |

Storage, Clocking |

1 due |

|

Multiplier |

| 4 |

Tue 9/14 |

Finite State Machines |

|

Simple ALU (PC1) due |

|

| 4 |

Thu 9/16 |

ISAs and MIPS |

|

|

FSM |

| 5 |

Tue 9/21 |

ISAs and MIPS |

|

|

|

| 5 |

Thu 9/23 |

ISAs and MIPS |

|

Full ALU (PC2) due |

Behavioral Verilog |

| 6 |

Tue 9/28 |

Datapaths |

2 due |

|

|

| 6 |

Thu 9/30 |

FPGAs + Datapaths |

|

|

FPGA Board Intro |

| 7 |

Tue 10/5 |

NO CLASS (Fall Break) |

|

|

|

| 7 |

Thu 10/7 |

Clock Division + Exam Practice Problems

|

3 due |

Register File (PC3) due |

I/O Interfacing: PS2 |

| 8 |

Tue 10/12 |

Exam 1 Review

|

|

|

|

| 8 |

Thu 10/14 |

Pipelining |

|

|

Exam 1

|

| 9 |

Tue 10/19 |

Exam 1 Muddiest Points

|

|

|

|

| 9 |

Thu 10/21 |

Pipelining |

|

|

Work on processor |

| 10 |

Tue 10/26 |

Memory Hierarchy |

|

Simple Processor (PC4) due |

|

| 10 |

Thu 10/28 |

Memory Hierarchy |

|

|

I/O Interfacing: VGA |

| 11 |

Tue 11/2 |

Memory Hierarchy |

|

|

|

| 11 |

Thu 11/4 |

Memory Hierarchy |

|

|

Work on processor |

| 12 |

Tue 11/9 |

Virtual Memory |

4 due |

|

|

| 12 |

Thu 11/11 |

Virtual Memory + Interrupts and Exceptions |

|

|

Q&A Session

|

| 13 |

Tue 11/16 |

OS |

5 due |

|

|

| 13 |

Thu 11/18 |

I/O + Exam 2 Review

|

|

Full Processor (PC5) due |

Exam 2

|

| 14 |

Tue 11/23 |

NO CLASS |

|

|

|

| 16 |

Fri 12/10 |

|

|

|

Final Project (PC6) Demo

|