ECE/COMPSCI 350L: Digital Systems — Spring 2019

Class meeting time and location: TTh 1:25–2:40, LSRC A247

Lab meeting time and location: T 3:05–6:05, W 1:25–4:25, W 4:40–7:40, Th 3:05–6:05, F 10:05–1:05, Hudson Hall 202A

Instructor: Dr. Rabih Younes

Duke e-mail: rabih.younes

Office: Hudson Hall 204

Office phone: 660-5051

Office hours: T 2:55–3:55 and W 10:45–11:45, or by appointment (the link to make appointments is posted on Sakai)

To provide anonymous feedback about anything related to the course: follow this link.

TAs:

- Kyle Finke (kwf10) — Head TA

- Liz Pharis (eap42) — Head Grading TA

- Conor McAvoy (cgm26) — Tuesday Lab TA

- Jack Fitzpatrick (jcf44) and August Ning (atn13) — Wednesday@1:25 Lab TAs

- Matt Dickson (mdd36) — Wednesday@4:40 Lab TA

- Vishnu Gottiparthy (vtg4) — Thursday Lab TA

- Siyuan Chen (sc456) — Friday Lab TA

- Nathaniel Brooke (neb17)

- Mary Stuart Elder (mse18)

- Natalie Huffman (nch15)

- Ken Koch (kek33)

- Dylan Powers (ddp19)

- Joseph Saldutti (jws61)

- Michael Scruggs (mts40)

TAs office hours (location: Hudson Hall 202A):

-

M 4–8:

- 4–6: Liz and Nathaniel

- 6–8: Mary Stuart and Joe

-

T 5–8:

- 5–6: Joe and Jack

- 6–8: Mike and Jack

-

W 4–8:

- 4–6: August and Dylan

- 6–8: Nat & Mary Stuart

-

Th 4–8:

- 4–6: Liz (priority for lecture-related questions)

- 5–6: August and Mike

- 6–8: Jack and Mike

Course Description

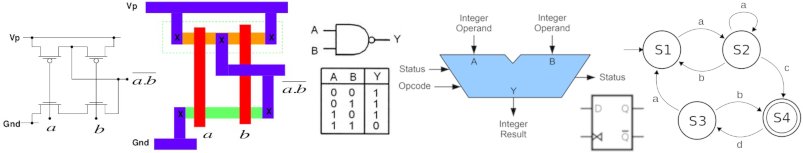

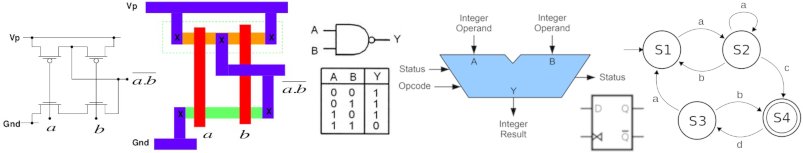

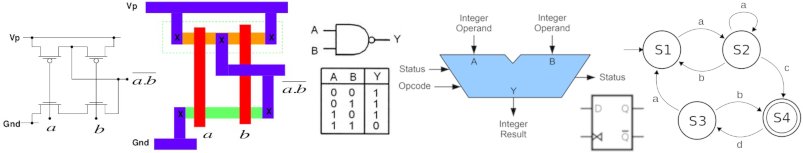

Design and implementation of combinational and sequential digital systems with special attention to digital computers. The use of computer-aided design tools, hardware description languages, and programmable logic chips to facilitate larger and

higher performance designs will be stressed. Laboratory exercises and group design projects will reinforce the various design techniques discussed in class. Prerequisite: Electrical and Computer Engineering 250D. Instructor: Younes. One course.

Learning Outcomes

Having successfully completed this course, the student will be able to:

- perform boolean algebra operations;

- design combinational and sequential circuits at the circuit (CMOS) and gate/logic levels;

- implement logic circuits on breadboards and FPGAs;

- interface with an FPGA using a variety of I/O components;

- use Verilog hardware description language; and

- design and implement a pipelined processor with an application running on it.

Textbook and Other Course Material

No textbook is required for this course. All material will be posted on Sakai (DO NOT repost/upload to any site; the material is copyrighted). I will always try to have slides posted before class time so that you can take notes on them if you

would like to.

Grading Policy

- Homeworks (10%): About one homework every two weeks (check the schedule below). The lowest grade will be dropped.

- Quizzes (-1% per missed quiz): Short pop quizzes. The objective of having these quizzes is to make sure you attend class and to prepare you for the exams.

- Exam 1 (20%): Tentatively on 2/26. Covers weeks 1–6. Long. Closed book/notes.

- Exam 2 (15%): Tentatively on 4/16. Covers weeks 8–14. Shorter than Exam 1. Closed book/notes.

- Labs (10%): Completed in groups of two during lab section. Grades are based on completion (must demonstrate working circuit/module to lab TA). You are not allowed to switch lab sections unless you have a valid excuse. You may come to

other lab sections and office hours to finish up an incomplete lab assignment; make sure you communicate that with the corresponding labs' TAs.

- Project checkpoints 1–4 (15%): Checkpoints to build a pipelined processor (regfile [1%], ALU [2%], multdiv [4%], and processor [8%]). Written in Verilog (hardware description language).

- Project checkpoints 5–10 (30%): Include project proposal, demo, report, and other project checkpoints in between. The final project is open-ended, in groups of two, and it includes the use of Verilog and Assembly.

- NO FINAL EXAM!

- Completion (-10%): All the above items require completion — as determined by the instructor/TAs — by the end of the semester. Even if you miss the deadline for an assignment (except for quizzes), you still must complete it

and submit it. Otherwise, your final course grade will be reduced by a full letter grade.

- Late policy: Late submissions are not allowed unless you have a valid excuse. In that case, contact the Head TA (CC me) about it as soon as possible and wait for a decision. Refer to this list of common but unacceptable excuses borrowed from Dr. Bletsch's webpage.

- Regrading policy: Regrade requests must be submitted no later than one week after the assignment grade is released.

Important Notes

***Extremely important advice: This course is historically known to have a very heavy load compared to other courses.

- Start as early as you can!

- Leave ample time for testing!

Another important advice: Try to always review slides the evening (or next day) of every class.

All announcements are posted on Piazza. Make sure you get Piazza email notifications.

Using git, Github, and LaTeX:

- Each pushed commit is considered a submission

- Code not associated with a commit is not accepted

- Submission time is when Github receives it

- Each commit must follow academic conduct policies

- Use Overleaf for LaTeX

Install Quartus version 16 and use it for labs and assignments. Other Quartus versions might not be fully compatible with grading scripts.

Contacting the instructor and the TAs:

- For questions that can be answered by any TA or the instructor: use Piazza

- To contact a specific TA or the instructor: use email (do not text, facebook, ...)

- To ask TAs about homeworks and grading: email the Head Grading TA (Liz)

- To ask TAs about other administrative issues: email the Head TA (Kyle)

Misconduct

- Academic misconduct will not be tolerated and will be taken very seriously.

- You are expected to complete the assignments individually unless otherwise stated.

- Students are encouraged to share ideas, learn from each other, and learn from online sources, but cheating is not tolerated.

- Any borrowed design/code/etc. — if allowed to be borrowed — should be properly cited.

- Students suspected violating the Duke Community Standard will be reported to the Office of Student Conduct.

- In addition to the measures taken by the Office of Student Conduct, the affected assignment(s) will receive zero credit, or possibly -100% in extreme cases.

- If you are considering this course of action, please see me instead, and we can work something out! I want every student in my course to be successful.

- Note that programming submissions will be compared to one another and to previous semesters using Stanford's Measure of Software Similarity (MOSS) to detect signs of plagiarism.

Summary of Important Dates

- 2/26: Exam 1

- 4/16: Exam 2

- 4/23: Project demo due

- 4/24: Project report due

| Week |

Date |

Topic |

Homework |

Project |

Lab |

| 1 |

1/10 |

Syllabus, Intro, Boolean Algebra |

|

|

|

| 2 |

1/15 |

Boolean Algebra, CAD & Verilog |

|

|

Lab 1 — Intro & Verilog Workshop |

| 2 |

1/17 |

CAD & Verilog, Registers |

|

|

|

| 3 |

1/22 |

Logic Blocks |

|

|

Lab 2 — Regfile |

| 3 |

1/24 |

Signed Arithmetic |

|

|

|

| 4 |

1/29 |

Fast Adders & ALU |

|

PC 1 (regfile) due |

Lab 3 — RCA |

| 4 |

1/31 |

Multipliers |

1 due |

|

|

| 5 |

2/5 |

Booth's Algorithm, Division |

|

PC 2 (alu) due |

Lab 4 — Comparators |

| 5 |

2/7 |

Memory Elements |

|

|

|

| 6 |

2/12 |

Pipelining: Intro, Hazards |

2 due |

|

Lab 5 — Memory |

| 6 |

2/14 |

Pipelining |

|

|

|

| 7 |

2/19 |

Guest Lecture by Dr. Tyler Bletsch: Miscellaneous Tips for Developing Digital Systems |

|

PC 3 (multdiv) due |

Lab 6 — VGA and PS2 |

| 7 |

2/21 |

Review Session 1

|

3 due |

|

|

| 8 |

2/26 |

Exam 1 (weeks 1–6)

|

|

|

Lab 7 — Audio |

| 8 |

2/28 |

Factorization |

|

|

|

| 9 |

3/5 |

Factorization, Quine-McCluskey |

|

|

Lab 8 — ADC |

| 9 |

3/7 |

FSM |

4 due |

|

|

| 10 |

3/12 |

NO CLASS: Spring Recess |

|

|

|

| 10 |

3/14 |

NO CLASS: Spring Recess |

|

|

|

| 11 |

3/19 |

FSM |

|

PC 4 (proc) due / defense |

Catch up |

| 11 |

3/21 |

FSM |

|

PC 5 (proposal) due |

|

| 12 |

3/26 |

Asynchronous Design |

|

|

Lab 9 — Project |

| 12 |

3/28 |

Asynchronous Design |

|

PC 6 (check in) due |

|

| 13 |

4/2 |

CMOS Design |

5 due |

|

Lab 10 — FSMs |

| 13 |

4/4 |

CMOS Design, Defect Tolerance |

|

PC 7 (check in) due |

|

| 14 |

4/9 |

Testing |

|

|

|

| 14 |

4/11 |

Review Session 2

|

6 due |

PC 8 (check in) due |

|

| 15 |

4/16 |

Exam 2 (weeks 8–14)

|

|

|

Project Work |

| 15 |

4/18 |

NO CLASS (read "Gate Arrays" slides) |

|

|

|

| 16 |

4/23 |

Project demos

|

|

PC 9 (demo) due |

Project Work |

| 16 |

4/24 |

Project demos

|

|

PC 10 (report) due |

|

| 17 |

5/3 |

NO FINAL EXAM |

|

|

|