| Week | Date | Topic | Quiz | Homework | Project | Lab |

|---|---|---|---|---|---|---|

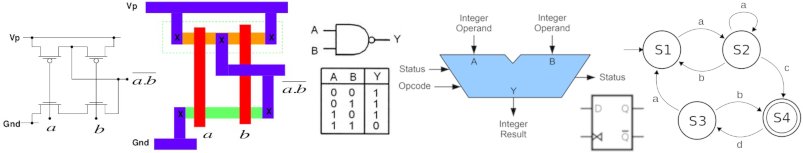

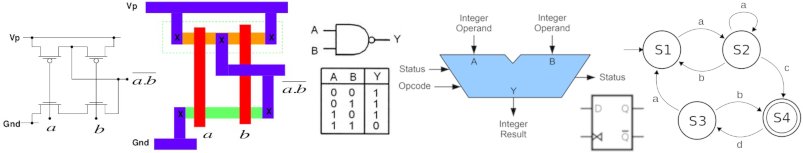

| 1 | 8/28 | Syllabus, Intro, Boolean Alg. | Lab 1 - Intro | |||

| 1 | 8/30 | Boolean Alg. | ||||

| 2 | 9/4 | Logic Blocks | 1 | 1 due | Lab 2 - Regfile | |

| 2 | 9/6 | CAD & Verilog, Register | Lab 1 Report Due | |||

| 3 | 9/11 | Signed Arithmetic | 2 | 2 due | PC 1 (regfile) due | Lab 3 - RCA |

| 3 | 9/13 | NO CLASS: Hurricane | Lab 2 No Report | |||

| 4 | 9/18 | Fast Adders & ALU, Multipliers | Lab 4 - Comparators | |||

| 4 | 9/20 | Booth's Algorithm, Division | 3 | 3 due | PC 2 (alu) due | Lab 3 Report Due |

| 5 | 9/25 | Memory Elements | 4 | Lab 5 - Memory | ||

| 5 | 9/27 | Memory Elements | 4 due | Lab 4 Report Due | ||

| 6 | 10/2 | Pipelining: Intro, Hazards | 5 | Lab 6 - VGA and PS2 | ||

| 6 | 10/4 | Pipelining | 5 due | PC 3 (multdiv) due | Lab 5 Report Due | |

| 7 | 10/9 | NO CLASS: Fall Break | No lab | |||

| 7 | 10/11 | Review Session 1 | 6 | 6 due | ||

| 8 | 10/16 | Exam 1 (weeks 1–6) | Lab 7 - Audio | |||

| 8 | 10/18 | Factorization | Lab 6 Report Due | |||

| 9 | 10/23 | Factorization, Quine-McCluskey | Lab 8 - ADC | |||

| 9 | 10/25 | FSM | 7 | 7 due | Lab 7 Report Due | |

| 10 | 10/30 | FSM | PC 4 (proc) due / defense | Catch up | ||

| 10 | 11/1 | FSM, Async. Design | 8 due | PC 5 (proposal) due | ||

| 11 | 11/6 | Async. Design | 8 | Lab 9 - Project | ||

| 11 | 11/8 | Async. Design, CMOS Design | 9 due | PC 6 (check in) due | Lab 8 Report Due | |

| 12 | 11/13 | CMOS Design, Defect Tolerance | 9 | Lab 10 - FSMs | ||

| 12 | 11/15 | Defect Tolerance, Testing | 10 due | PC 7 (check in) due | ||

| 13 | 11/20 | NO CLASS (go through the "Gate Arrays" lecture) | Lab 10 Report Due | |||

| 13 | 11/22 | NO CLASS: Thanksgiving | ||||

| 14 | 11/27 | Review Session 2 | 10 | 11 due | PC 8 (check in) due | Project Work |

| 14 | 11/29 | Exam 2 (weeks 8–12) | ||||

| 15 | 12/6 | Project demos | PC 9 (demo) due | Project Work | ||

| 15 | 12/7 | Project demos | PC 10 (report) due | |||

| 16 | 12/14 | NO FINAL EXAM |